- RS Stock No.:

- 697-9016

- Mfr. Part No.:

- KSZ8851-16MLL-EVAL

- Brand:

- Micrel

Discontinued product

- RS Stock No.:

- 697-9016

- Mfr. Part No.:

- KSZ8851-16MLL-EVAL

- Brand:

- Micrel

Technical Reference

Legislation and Compliance

Product Details

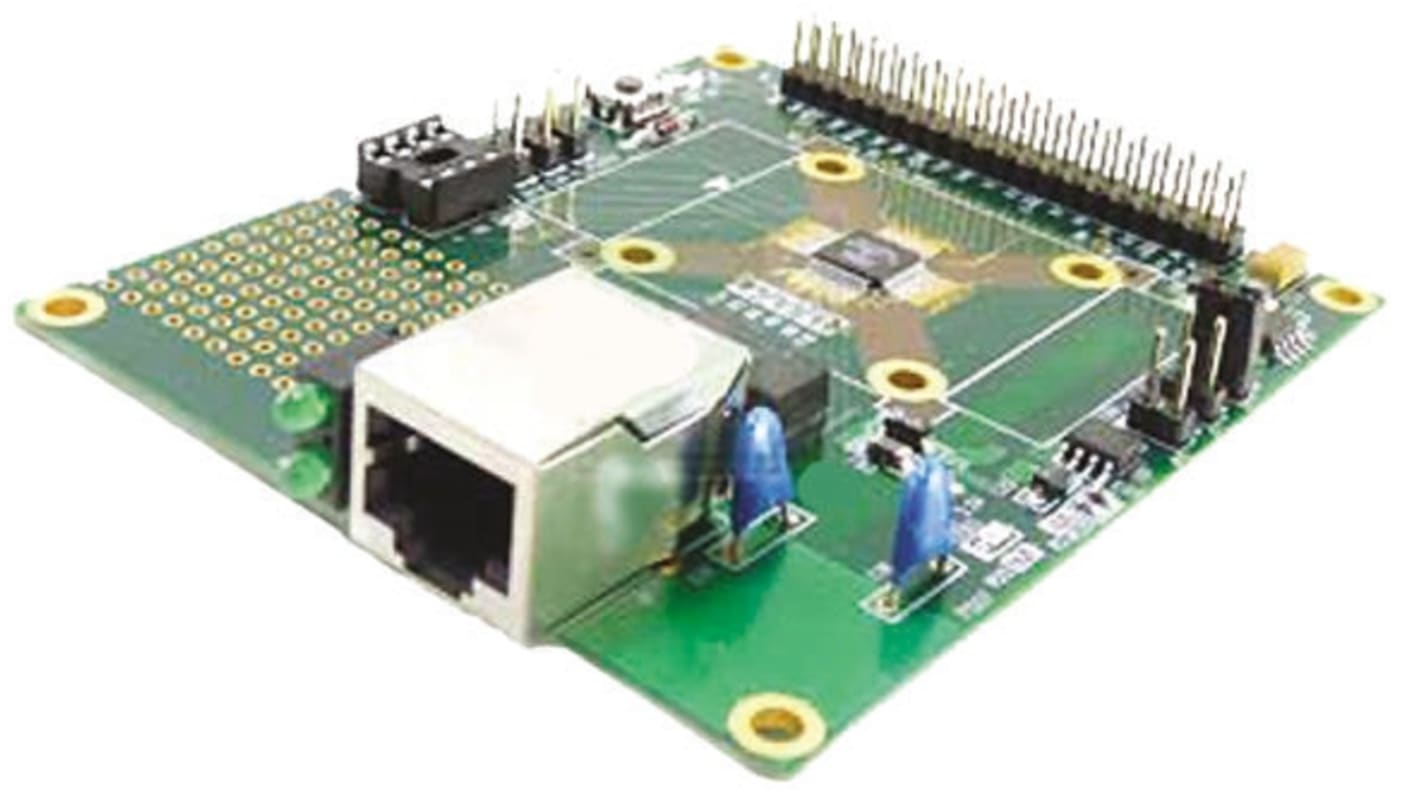

Evaluation Board for KSZ8851 Series

The KSZ8851 is a single-chip Fast Ethernet controller consisting of a 10/100Base-T physical layer transceiver (PHY), a MAC, and a microprocessor interface.

Integrated MAC and PHY Ethernet controller fully compliant with IEEE 802.3/802.3u standards

Designed for high performance and high throughput applications

Supports 10Base-T/100Base-TX

Supports IEEE 802.3x full-duplex flow control and half-duplex backpressure collision flow control

Supports DMA-slave burst data read and write transfers

Supports IP Header (IPv4)/TCP/UDP/ICMP checksum generation and checking

Automatic 32-bit CRC generation and checking

Simple SRAM-like host interface easily connects to most common embedded MCUs

Supports multiple data frames for transmit and receive without address bus and byte-enable signals

Supports both Big- and Little-Endian processors

Larger internal memory with 12KBytes for RX FIFO and 6K Bytes for Tx FIFO

Programmable low, high and overrun watermark for flow control in Rx FIFO

Efficient architecture design with configurable host interrupt schemes to minimize host CPU overhead and utilization

Powerful and flexible address filtering scheme

Single 25MHz reference clock for both PHY and MAC

Designed for high performance and high throughput applications

Supports 10Base-T/100Base-TX

Supports IEEE 802.3x full-duplex flow control and half-duplex backpressure collision flow control

Supports DMA-slave burst data read and write transfers

Supports IP Header (IPv4)/TCP/UDP/ICMP checksum generation and checking

Automatic 32-bit CRC generation and checking

Simple SRAM-like host interface easily connects to most common embedded MCUs

Supports multiple data frames for transmit and receive without address bus and byte-enable signals

Supports both Big- and Little-Endian processors

Larger internal memory with 12KBytes for RX FIFO and 6K Bytes for Tx FIFO

Programmable low, high and overrun watermark for flow control in Rx FIFO

Efficient architecture design with configurable host interrupt schemes to minimize host CPU overhead and utilization

Powerful and flexible address filtering scheme

Single 25MHz reference clock for both PHY and MAC

Ethernet Communications - Microchip

Specifications

Attribute | Value |

|---|---|

| Kit Classification | Evaluation Board |