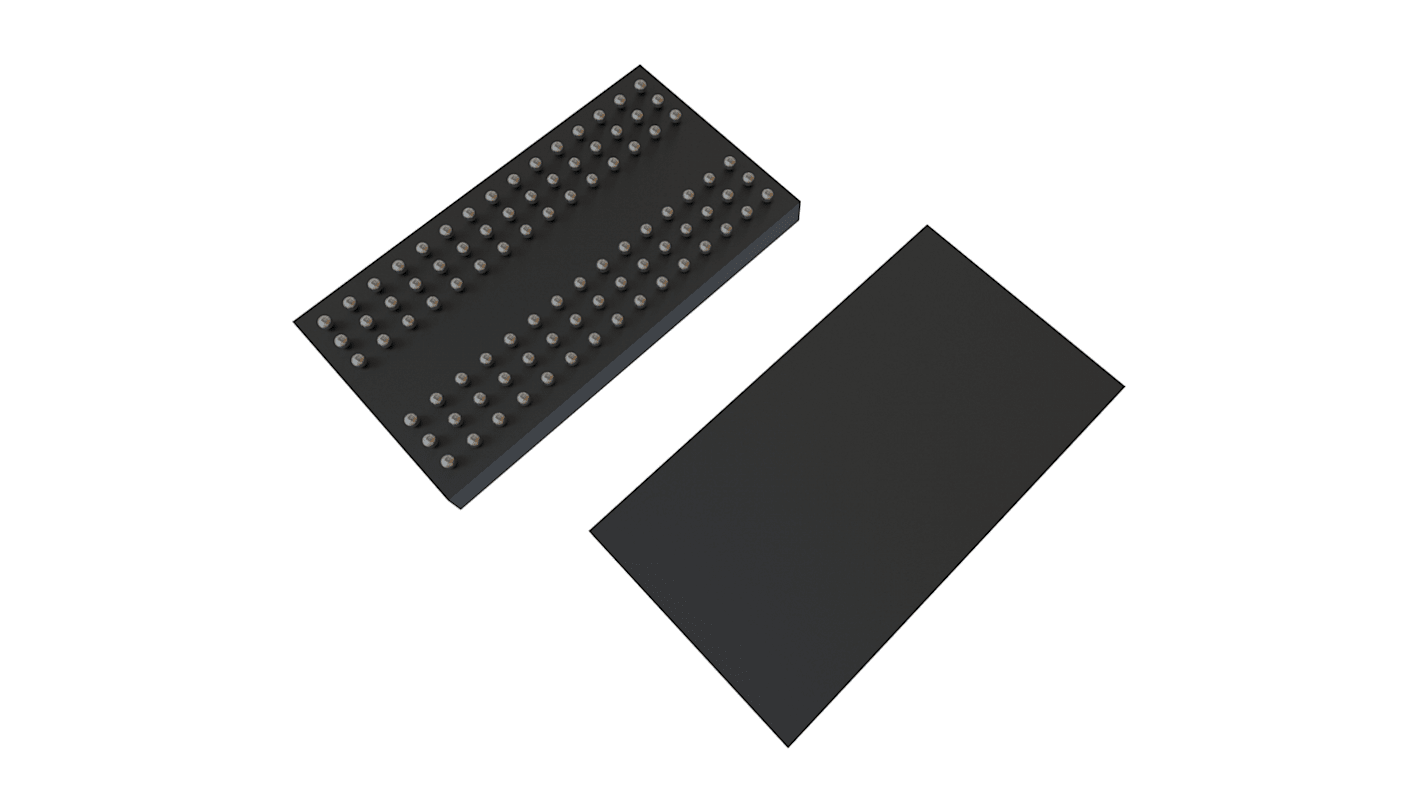

Winbond DDR2 SDRAM 128 MB Surface, 84-Pin 16 bit TFBGA

- RS Stock No.:

- 188-2580

- Mfr. Part No.:

- W9712G6KB25I

- Brand:

- Winbond

Subtotal (1 tray of 209 units)*

Kr. 4 239,356

(exc. VAT)

Kr. 5 299,195

(inc. VAT)

FREE delivery for online orders over 750,00 kr

Temporarily out of stock

- Shipping from 22 September 2026

Need more? Click ‘Check delivery dates’ to find extra stock and lead times.

Units | Per unit | Per Tray* |

|---|---|---|

| 209 + | Kr. 20,284 | Kr. 4 239,36 |

*price indicative

- RS Stock No.:

- 188-2580

- Mfr. Part No.:

- W9712G6KB25I

- Brand:

- Winbond

Specifications

Technical Reference

Legislation and Compliance

Product Details

Find similar products by selecting one or more attributes.

Select all | Attribute | Value |

|---|---|---|

| Brand | Winbond | |

| Memory Size | 128MB | |

| Product Type | DDR2 SDRAM | |

| Data Bus Width | 16bit | |

| Address Bus Width | 15bit | |

| Number of Bits per Word | 8 | |

| Maximum Random Access Time | 0.4ns | |

| Number of Words | 16M | |

| Mount Type | Surface | |

| Package Type | TFBGA | |

| Pin Count | 84 | |

| Minimum Operating Temperature | -40°C | |

| Maximum Operating Temperature | 95°C | |

| Standards/Approvals | RoHS | |

| Series | W9712G6KB | |

| Length | 12.6mm | |

| Height | 0.8mm | |

| Maximum Supply Voltage | 1.9V | |

| Automotive Standard | No | |

| Minimum Supply Voltage | 1.7V | |

| Supply Current | 135mA | |

| Select all | ||

|---|---|---|

Brand Winbond | ||

Memory Size 128MB | ||

Product Type DDR2 SDRAM | ||

Data Bus Width 16bit | ||

Address Bus Width 15bit | ||

Number of Bits per Word 8 | ||

Maximum Random Access Time 0.4ns | ||

Number of Words 16M | ||

Mount Type Surface | ||

Package Type TFBGA | ||

Pin Count 84 | ||

Minimum Operating Temperature -40°C | ||

Maximum Operating Temperature 95°C | ||

Standards/Approvals RoHS | ||

Series W9712G6KB | ||

Length 12.6mm | ||

Height 0.8mm | ||

Maximum Supply Voltage 1.9V | ||

Automotive Standard No | ||

Minimum Supply Voltage 1.7V | ||

Supply Current 135mA | ||

The W9712G6KB is a 128M bits DDR2 SDRAM and speed involving -25, 25I and -3.

Double Data Rate architecture: two data transfers per clock cycle

CAS Latency: 3, 4, 5 and 6

Burst Length: 4 and 8

Bi-directional, differential data strobes (DQS and /DQS ) are transmitted / received with data

Edge-aligned with Read data and center-aligned with Write data

DLL aligns DQ and DQS transitions with clock

Differential clock inputs (CLK and /CLK)

Data masks (DM) for write data

Commands entered on each positive CLK edge, data and data mask are referenced to both edges of /DQS

Posted /CAS programmable additive latency supported to make command and data bus efficiency

Read Latency = Additive Latency plus CAS Latency (RL = AL + CL)

Off-Chip-Driver impedance adjustment (OCD) and On-Die-Termination (ODT) for better signal quality

Auto-precharge operation for read and write bursts

Auto Refresh and Self Refresh modes

Precharged Power Down and Active Power Down

Write Data Mask

Write Latency = Read Latency - 1 (WL = RL - 1)

Interface: SSTL_18

Related links

- Winbond DDR2 SDRAM 128 MB Surface, 84-Pin 16 bit TFBGA

- Winbond W9712G6KB25I DDR2 SDRAM 128 MB Surface, 84-Pin 16 bit TFBGA

- Winbond SDRAM 128 MB Surface, 54-Pin 16 bit TSOP

- Micron SDRAM 128 MB Surface, 54-Pin 16 bit TSOP

- Alliance Memory SDRAM 128 MB Surface, 54-Pin 16 bit TSOP

- ISSI IS42S16800F-7TL SDRAM 128 MB Surface, 54-Pin 16 bit TSOP

- Winbond SDRAM 512 MB Surface, 84-Pin 16 bit VFBGA

- Alliance Memory AS4C8M16SA-7TCNTR SDRAM 128 MB Surface, 54-Pin 16 bit TSOP